Последната актуализация на този раздел е от 2020 година.

5.1.1 Структура на

операционната част на машинната команда

След като в предидущия параграф

дефинирахме и отчасти пояснихме основополагащото множество от понятия,

неизбежно свързани с изучаването на компютъра, от тук нататък поясненията ще се

задълбочават и ще станат по-конкретни. Поради особеното значение на понятието машинна

команда тук започваме с него. В хода на изчислителния процес (т.е. при

изпълнение на програмата), посочването на всяка поредна операция става в “Поле 1” на машинната команда (вижте фигура 5.1.2). Както беше пояснено, в това поле се

съдържа единствено възможното изразно средство – двоична комбинация. Известно е, че броят N на

възможните в едно поле двоични комбинации зависи от неговата дължина (от

неговата разрядност), означена например с n[b], т.е. броят на комбинациите се определя чрез

известната формула: N=2n. Така при предварително известен брой на

изпълнимите в един процесор операции, минималната дължина на двоичната комбинация,

която еднозначно ще изразява всяка отделна операция, се определя от посочената

вече формула така: n=ëlog2(N)û.

Тази комбинация има смисъла на код – понятие, което

определихме в §1.1.

Изобразяваната

в “Поле 1” от структурата на командата двоична комбинация, поради ясната си

функционалност, има точно определено наименование – код

на операцията (КОП). Така често ще казваме, че в операционната част

на командата се намира кодът на операцията. Читателят навярно разбира, че един

8-разряден двоичен код може еднозначно да кодира до 256 различни операции.

Както показва практиката, обемът на множеството изпълними операции за

различните модели процесори се движи най-често в интервала от 50 до 200, което

означава, че типичната дължина на полето КОП е 8 бита. В някои реални процесори обаче, с цел облекчаване на

декодирането, кодът на операцията е удължен умишлено, като са добавени още 1

или 2 байта, което означава, че дължината на операционната част на машинната

команда в общия случай е променлива.

Кодът на

операцията може да бъде хомогенен, т.е. интерпретиран цялостно (от край

до край). В повечето реални случаи обаче той е структуриран, т.е.

нехомогенен. Във втория случай двоичната комбинация КОП е възможно да бъде

съставена от няколко части със собствена функционалност (собствена

интерпретация), наречени спецификатори. Така кодът на операцията може да

се определи като краен списък от спецификатори:

КОП < С1,

С2, С3, … > .

На

практика спецификаторите (С1,С2,...) са различни по смисъл и брой. Съществуват

системи от машинни команди, в които полето на КОП е постоянно по дължина и винаги съдържа едни и същи

спецификатори, но съществуват и системи, в които полето на КОП не е постоянно и за някои

специални команди може да се удължава или скъсява. Списъкът от спецификатори в

отделните команди е различен и променлив. Самите спецификатори, като елементи в

структурата на командата, също могат да бъдат с променлива дължина, изменяща се

за сметка на липсващите такива.

Типични спецификатори са:

а) Спецификатор за тип на командата.

Този спецификатор (двоична комбинация от два или три бита) определя

структурата, дължината и общата интерпретация на командата от гледна точка на

трансфера на информацията, свързана с действието. Повечето команди са:

·

От тип "регистър-регистър" (RG-RG);

·

От тип "регистър-памет" (RG-Mem);

·

От тип "памет-памет" (Mem-Mem);

·

От тип "за преход" (Jump);

·

От тип "други".

Командите

от тип "регистър-регистър"

са онези, които посочват (адресират) своите операнди най-често в програмно достъпните

възли (регистри) на логическата структура на процесора. Преди всичко това са

регистрите с общо предназначение, откъдето произтича и наименованието на типа

им. Поради малкия брой на регистрите в структурата на процесорите, адресирането

им се постига с двоична комбинация, чиято дължина е малка и обикновено е в

пределите от 3 до 5 бита. Ако адресът на регистър например е с дължина 4 бита

(с възможност за адресиране максимум на 16 регистъра), то за посочване на

операндите на една двуместна операция са необходими общо 8 бита. Така машинните

команди от този тип имат малка дължина, заемат малко място в паметта, извличат

се в рамките на едно обръщение към паметта и се изпълняват бързо, тъй като имат

непосредствен достъп до операндите. С други думи, командите от тип

“регистър-регистър”, имат съществени достойнства в смисъла на критерия за

бързодействие.

Командите

от тип "регистър-памет"

и "памет-памет"

са с по-сложна структура и се изпълняват по-бавно, тъй като единият или и двата

операнда на заповяданото действие се извличат от оперативната памет.

Многократното обръщение на командата към паметта при доставяне на операндите

забавя изпълнението на операцията. Тук е необходимо да уточним, че този

недостатък се изявява в процесори с по-елементарна архитектура. В процесори с

развита архитектура на запомнящата система, изказаното качество на този тип

команди, не бива да се възприема буквално. Архитектурата на съвременната

запомняща система е йерархична (вижте глава 6).

В нея е налице йерархична буферна памет (кеш памет), а наличието на такава

система в структурата на процесора е причина за коренна промяна на

микропрограмните процедури за достъп до данни. Въпреки това необходимо е да

споменем, че дори и в такива системи има един случай, когато казаното по-горе

има смисъл. Това е ситуация на кеш-пропуск, когато в условия на виртуална

памет, в следствие на отсъствие на заявената страница, съдържаща предявения

адрес, закъснението е възможно да бъде много по-съществено от едно обикновено

обръщение към паметта. Алгоритмичните и структурните особености на запомнящата

система, както и свързаните с тях скоростни оценки, са разгледани в глава 6 на

тази книга.

б) Спецификатор за форма и формат на операндите. В практиката, с цел да

придадат универсални качества на процесорите, производителите създават

възможност една и съща операция да се изпълнява върху операнди с различна

дължина, т.е. операнди с различни формати, но с една и съща форма, например с

фиксирана запетая (вижте фигура 1.1.6.1.3).

Така за всяка отделна операция се получава едно подмножество от различни

машинни команди. Например, в процесори с 32-битова разрядна мрежа, за числа

представени във форма с фиксирана запетая, са възможни:

·

Набор машинни команди за събиране на 8-битови

операнди ;

·

Набор машинни команди за събиране на 16-битови

операнди и ;

·

Набор машинни команди за събиране на 32-битови

операнди.

Въпреки че

операцията е една и съща, различните формати на данните изискват различни

машинни команди. Това е така, защото отделните формати изискват различно

управление на логическата структура на съответното устройство. От гледна точка

на техническата реализация на операцията върху различни формати на операндите,

е необходимо да обърнем внимание на читателя, че логическите функции, формиращи

признаците на резултата, е възможно да не приемат актуални стойности. Ако

например се събират 8-битови числа с фиксирана запетая в допълнителен код в

едно 32-битово устройство за събиране, то функциите (1.2.3),

(1.6.2.18), (1.6.2.19),

(1.6.3.2) за откриване на препълване V, както и функциите за

признаците S, C, P и други (вижте фигура

3.2.1.1) е възможно да не генерират актуални (смислени) стойности. За да

бъдат тези стойности актуални признаци на резултата, при проектиране на

процесора логическите функции на признаците следва да се поставят в зависимост

от форматите на операндите, които даденият процесор ще поддържа, или още в

зависимост от формáта, който текущата машинна команда указва. Признакът Z за нулев резултат обаче е

инвариантен към формата на операндите с фиксирана запетая в условията на

допълнителен код. Казаното има своя смисъл и за всички изпълними операции. По

принцип казаното току що поставя пред конструктора на процесора задачата за

формиране на признаците на резултата е един много по-широк смисъл, като при

това й придава съществена сложност.

Що се отнася до фόрмата, в която са представени числата, в качеството им на операнди, това е признак, по който се образува едно друго подмножество машинни команди (КОП) за всяка отделна операция. Ако по-горе споменахме операндите като числа във форма с фиксирана запетая, то не можем да пропуснем тези във форма с плаваща запетая. Както вече изяснихме (вижте таблица 1.1.6.2.1), числата в тази форма също имат различни формати. Нещо повече, възможни са и различни структури на представяне (вижте фигури 1.1.6.2.2 и 1.1.6.2.3). Всички машинни команди в процесорите Intel например, които използват операнди, представени във форма с плаваща запетая, се разпознават по това, че техният код на операцията (вижте по-долу фигура 5.1.1.1) започва с двоичната комбинация 11011, т.е. (Opcode[7¸3])=11011.

в) Спецификатор на същинския код на операцията. Това е онази част от

двоичната комбинация в полето КОП, която пряко съответства на общия смисъл

(същност) на заповяданата от командата операция. Тя в най-голяма степен

конкретизира избора (декодирането) на алгоритъм за управление от страна на

управляващото устройство. Винаги се съдържа в първия (по ред на извличане) байт

на машинната команда.

г) Спецификатор за разширение на КОП. В някои процесори с цел

по-лесно декодиране на командата, т.е. за избор на управляващия алгоритъм, се

прилага удължаване на операционната част на машинната команда (вижте фигура 5.1.2), обикновено с още един или два байта.

За целта този факт се указва допълнително. Това дава възможност общата дължина

на командата да се определя по време на нейното изтегляне от оперативната

памет.

д) Спецификатор за превилегированост на

командата.

При наличието на такъв спецификатор става възможно изграждането на по-надеждно

програмно осигуряване, тъй като командата поставя предварителни условия за

своето изпълнение – въпрос на който ще се спрем по-късно в тази глава.

е) Спецификатор за циклическо повторение. Този спецификатор е

свързан с особено изпълнение на регистъра на командата. Обикновено той присъствува

в командни системи на процесори, в които е реализиран така наречения команден

буфер, който се разглежда подробно в следващата 6-та глава на тази книга.

Съвременните процесори като правило се характеризират с реализацията си върху

значително по-сложни алгоритмични схеми за организация на функционирането си, в

сравнение с класическата, която ние представихме в предидущия пункт. Това се

дължи преди всичко на изключителните възможности на съвременните технологии.

Тук ще посочим само два факта отнасящи се до тази организация:

·

В съвременните процесори трансферът на машинни

команди от оперативната памет към буферната памет се извършва в порции

(блокове), чийто обем е значителен (например 32 байта) и които порции съдържат

голям брой машинни команди. Процесът на извличане в тези условия е напълно асинхронен

по отношение на изпълнението на операциите. В този смисъл командният цикъл,

като основен организационен алгоритъм, се постига като разпределен в различни

устройства ;

·

Извлечените от

оперативната памет машинни команди се “складират” в командния буфер, където

очакват своето изпълнение, т.е. извличането се характеризира като изпреварващо.

С други думи, в смисъла на командния цикъл, самото извличане от оперативната

памет на командите изпреварва във времето самото им изпълнение.

При така

изказаните условия, повтарящите се в алгоритмичен цикъл машинни команди (като

група команди от дадена програма) има смисъл да бъдат маркирани със

спецификатор за циклическо повторение, с което дават възможност за консумиране

на допълнителен положителен ефект от факта, че копието на участъка от

програмата, съдържащ цикъла, се намира се в командния буфер, т.е. не се налага

непрекъснато извличане от ОП на повтарящите се команди.

ж) Други.

Спецификаторите могат да определят командата

както самостоятелно, така и в комбинация, като някои от стойностите на един

спецификатор могат да бъдат предназначени за изменение на смисъла на други

спецификатори. Съществуват системи от команди, в които определени спецификатори

са незадължителни и тяхното присъствие (или отсъствие) се определя от други

условия.

Примери

Като конкретни примери ще разгледаме структурата на полето на код на операцията в следните широко разпространени и описани в литературата системи:

1. Микропроцесори

на фирмата Intel.

Въпреки,

че фирма Intel произвежда цяла серия съвместими микропроцесори, кратко

ще представим събирателната архитектура iA-32. Тя е най-разпространената и

широко описаната и представлява един силно изразителен пример за темата, която

изясняваме. Не бихме желали да осветляваме тази тема с най-новите и

непрекъснато появяващи се процесори. Темата е принципно и достатъчно изяснена

от следващото изложение, а то е достатъчно като отправна база, ако читателят

пожелае допълнително и самостоятелно да изследва темата.

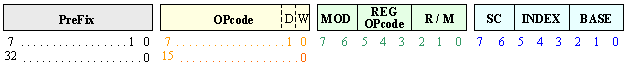

Според

общата структура на машинната команда, в нейната операционна част са предвидени

задължителни и незадължителни елементи. Абсолютно задължителен елемент се явява

поле с дължина 1 или 2 байта, съдържащо спецификатор на същинския код (OPcode). В някои машинни команди младшите

два бита на това поле имат отделно предназначение: спецификатор за

посока (D) и спецификатор за

формат на операндите (W), както

е показано по-долу на рисунката.

Фиг. 5.1.1.1. Елементи на структурата на операционната

част на iA-32-команда

Освен полето с КОП, операционната част на

машинната команда може да се следва от още един или от още два незадължителни

байта. Байтът, съдържащ КОП, се нарича Opcode-байт, съседният му отдясно

се нарича ModR/M-байт, а най-десният – SIB-байт. Специален вид

незадължителни елементи, наречени префикси,

е възможно да предхождат машинната команда.

Означенията в рисунката имат по-подробно следния смисъл:

·

Opcode – код на операцията. Младшите два бита в този

байт, отбелязани с букви W и D, в някои команди (не във всичките) могат да имат

интерпретацията, представена по-долу:

·

W – (Бит b0) – атрибут на размера:

ако (b0)=0 то размерът е

½ от дължината, т.е. 1 байт (L – младши, или H – старши) ;

в противен случай, когато (b0)=1, размерът

съответства на цялата дължина, т.е. 2 байта. Тази дължина е наречена дума (word).

Във фирмените означения, когато се има предвид точно тази дължина, същата се

означава чрез буквата Х. Така например с AL се означава младшия байт на

акумулатор А, с AH – старшия байт, а с AX – 2 младши байта (една дума) от

пълната 32-битова дължина на акумулатора. Тъй като архитектурата на процесора е

32-битова, то за означение на пълната 32-битовата дължина на регистрите

обикновено се добавя буква Е. Така 32-битовата дължина на акумулатор А се

означава с три букви: EAX ;

·

D – (Бит b1) – атрибут за направление:

определя даден регистър в структурата на процесора като предавател или приемник

на данни. В първия случай (b1)=0 от регистъра се четат данни (регистърът е източник),

а във втория случай, при (b1)=1 – в регистъра се записват данни (регистърът е

приемник). ;

·

MOD – поле на режима. Двоичната комбинация в

това поле определя дължината на отместването и заедно с комбинацията в полето

R/M определят 32 на брой различни схеми за адресация (8 регистрови и 24

индексни). Схемите за адресация при различна стойност на атрибута на размера са

представени в таблица 5.1.1.2 ;

·

R/M – означава register/memory . Когато

съдържанието на това поле се интерпретира като адрес (номер) на регистър, то

този регистър участва във формирането на изпълнителния адрес (EA – effective

address). В таблица 5.1.1.1 е показано адресирането (номерирането) на

регистрите.

Таблица 5.1.1.1 Адресиране на регистрите

|

reg8 |

AL |

CL |

DL |

BL |

AH |

CH |

DH |

BH |

|

reg16 |

AX |

CX |

DX |

BX |

SP |

BP |

SI |

DI |

|

reg32 |

EAX |

ECX |

EDX |

EBX |

ESP |

EBP |

ESI |

EDI |

|

REG |

000 |

001 |

010 |

011 |

100 |

101 |

110 |

111 |

Таблица 5.1.1.2 Схеми за изчисляване на ефективния адрес

според ModR/M-байт

|

(B)=0 |

|

|

(B)=1 |

|

Ефективен адрес |

MOD |

R / M |

Ефективен адрес |

|

(BX)+(SI) |

0 0 |

0 0 0 |

(EAX) |

|

(BX)+(DI) |

|

0 0 1 |

(ECX) |

|

(BP)+(SI) |

|

0 1 0 |

(EDX) I) |

|

(BP)+(DI) |

|

0 1 1 |

(EBX) I) |

|

(SI) |

|

1 0 0 |

(--) (--) |

|

(DI) |

|

1 0 1 |

disp32 |

|

disp16 |

|

1 1 0 |

(ESI) |

|

(BX) |

|

1 1 1 |

(EDI) |

|

(BX)+(SI) + disp8 |

0 1 |

0 0 0 |

(EAX) + disp8 |

|

(BX)+(DI) + disp8 |

|

0 0 1 |

(ECX) + disp8 |

|

(BP)+(SI) + disp8 |

|

0 1 0 |

(EDX) + disp8 |

|

(BP)+(DI) + disp8 |

|

0 1 1 |

(EBX) + disp8 |

|

(SI) + disp8 |

|

1 0 0 |

(--) (--)+ disp8 |

|

(DI) + disp8 |

|

1 0 1 |

(EBP) + disp8 |

|

(BP) + disp8 |

|

1 1 0 |

(ESI) + disp8 |

|

(BX) + disp8 |

|

1 1 1 |

(EDI) + disp8 |

|

(BX)+(SI) + disp16 |

1 0 |

0 0 0 |

(EAX) + disp32 |

|

(BX)+(DI) + disp16 |

|

0 0 1 |

(ECX) + disp32 |

|

(BP)+(SI) + disp16 |

|

0 1 0 |

(EDX) + disp32 |

|

(BP)+(DI) + disp16 |

|

0 1 1 |

(EBX) + disp32 |

|

(SI) + disp16 |

|

1 0 0 |

(--) (--)+ disp32 |

|

(DI) + disp16 |

|

1 0 1 |

(EBP) + disp32 |

|

(BP) + disp16 |

|

1 1 0 |

(ESI) + disp32 |

|

(BX) + disp16 |

|

1 1 1 |

(EDI) + disp32 |

|

EAX / AX / AL |

1 1 |

0 0 0 |

EAX / AX / AL |

|

ECX / CX / CL |

|

0 0 1 |

ECX / CX / CL |

|

EDX / DX / DL |

|

0 1 0 |

EDX / DX / DL |

|

EBX / BX / BL |

|

0 1 1 |

EBX / BX / BL |

|

ESP / SP / AH |

|

1 0 0 |

ESP / SP / AH |

|

EBP / BP / CH |

|

1 0 1 |

EBP / BP / CH |

|

ESI / SI / DH |

|

1 1 0 |

ESI / SI / DH |

|

EDI / DI / BH |

|

1 1 1 |

EDI / DI / BH |

Забележка:

Всички означения в този пример са предложените и използваните от фирма Intel.

Най-десният байт в рисунката от фигура

5.1.1.1 е предназначен да уточни допълнително схемата за адресиране (вижте

по-долу таблица 5.1.1.4) и съдържа три спецификатора, чийто смисъл е следния:

·

SC – съдържанието на това 2-битово поле определя

стойността (scale) на мащабния коефициент. Мащабният коефициент има

стойностите: 2=21, 4=22, 8=23 . Както се вижда

от формулата, полето съдържа степенния показател, т.е. някое от числата 0, 1, 2

или 3;

·

INDEX – определя номера (адреса) на индексен регистър

;

·

BASE – определя номера (адреса) на базов регистър,

според таблица 5.1.1.3.

Таблица 5.1.1.3 Базови регистри

|

reg32 |

EAX |

ECX |

EDX |

EBX |

ESP |

EBP |

ESI |

EDI |

|

BASE |

000 |

001 |

010 |

011 |

100 |

101 |

110 |

111 |

Таблица 5.1.1.4 Влияние на SIB-байт върху

съдържанието на регистрите

|

Мащабен индекс |

SC |

INDEX |

|

(EAX) |

0 0 |

0 0 0 |

|

(ECX) |

|

0 0 1 |

|

(EDX)I) |

|

0 1 0 |

|

(EBX)I) |

|

0 1 1 |

|

|

|

1 0 0 |

|

(EBP) |

|

1 0 1 |

|

(ESI) |

|

1 1 0 |

|

(EDI) |

|

1 1 1 |

|

(EAX*2) |

0 1 |

0 0 0 |

|

(ECX*2) |

|

0 0 1 |

|

(EDX*2) |

|

0 1 0 |

|

(EBX*2) |

|

0 1 1 |

|

|

|

1 0 0 |

|

(EBP*2) |

|

1 0 1 |

|

(ESI*2) |

|

1 1 0 |

|

(EDI*2) |

|

1 1 1 |

|

(EAX*4) |

1 0 |

0 0 0 |

|

(ECX*4) |

|

0 0 1 |

|

(EDX*4) |

|

0 1 0 |

|

(EBX*4) |

|

0 1 1 |

|

|

|

1 0 0 |

|

(EBP*4) |

|

1 0 1 |

|

(ESI*4) |

|

1 1 0 |

|

(EDI*4) |

|

1 1 1 |

|

(EAX*8) |

1 1 |

0 0 0 |

|

(ECX*8) |

|

0 0 1 |

|

(EDX*8) |

|

0 1 0 |

|

(EBX*8) |

|

0 1 1 |

|

|

|

1 0 0 |

|

(EBP*8) |

|

1 0 1 |

|

(ESI*8) |

|

1 1 0 |

|

(EDI*8) |

|

1 1 1 |

В представените таблици са употребени

следните означения:

1. disp8

(displace) –

представя 8-битово отместване, което след знаково разширение до 16 бита, се

събира с индекса;

2. disp16

– представлява 16-битово отместване, което се събира с индекса ;

3. disp32

– представлява 32-битово отместване, което се събира с индекса ;

Описаните

три байта, както вече споменахме, е възможно да се предхождат от незадължителни

префиксни елементи. Префиксните елементи имат дължина 1 байт. Те могат

да бъдат до 4 на брой, т.е. КОП на всяка машинна команда може да се предхожда

максимум от 4 байта, съдържащи следните видове префикси:

1. Префикс на командата.

Използува се за организиране на циклическо повторение на командата и за блокиране на шината на процесора. Означенията им (стойностите им) са:

REPºF3h

; REPE/REPZºF3h

; REPNE/REPNZºF2h

; LOCKºF0h

.

2. Префикс

за размер на адреса – 67h.

3. Префикс

за размер на данните – 66h.

Тези два

префикса осигуряват за процесора възможност да работи с 16- и 32-разрядни

адреси и данни. Префиксите работят като тригери – ако след тях командата работи

с 32-битови адреси или операнди, то процесорът ги интерпретира като 16-битови и

обратно.

4. Префикс

за избор (за подмяна) на сегментен регистър.

С този префикс изпълнението на машинната

команда може да се прехвърля в различни области на оперативната памет, тъй като

префиксът, който я предхожда подменя имащият се предвид по подразбиране

сегментен регистър с друг. Стойността на префикса определя името на новия

регистър:

2EhºCS (Code Segment); 36hºSS (Stack Segment); 3EhºDS (Data Segment);

26hºES (Extra Segment); 64hºFS и 65hºGS (допълнителни даннови сегменти) .

Без да

изпадаме в повече обяснения по дадения пример, вече можем да направим извода,

че този процесор има изключително развита система от спецификатори в

операционната част, водеща до голям брой машинни команди. При такава структура

на операционната част на командата същата, след своето извличане, трябва да

бъде напълно декодирана, за да стане ясно каква точно е операцията и колко

дълга е самата команда.

2. Микропроцесори на фирмата Motorola

Различни

модели 32-битови микропроцесори на тази фирма стоят в основата на много модели

персонални и специализирани компютърни системи, ето защо ще се спрем кратко и

на този пример, като поясним

базовия модел МС680ХХ. Машинната команда на този процесор има променлив формат

с обща дължина в границите от 2 до 12 байта, като първите два (старши) байта са

главните, тъй като те съдържат операционната й част. В първите два байта се

съдържа кодът на операцията, както и спецификатори за особеностите на

конкретната операция, допълващи същинския код, а така също отнасящи се за

операндите, за размерите им, за методите на адресиране и други. Когато първата

дума (първите 2 байта) е недостатъчна тази информация се прехвърля в следващата

дума. Структурата на операционното поле (първите 2 байта) на повечето машинни

команди е следната:

![]()

Фиг. 5.1.1.2. Операционната част на команда на базовия

процесор на Motorola MC680ХХ

Старшите четири бита на кода на операцията

(вижте горната рисунка) кодират 16 типа команди. Допълнителното разшифроване на

командата се постига чрез кодовете на специфичните за всеки тип команди

спецификатори. В техническата документация на процесорите на Motorola се

привежда логическата структура на всяка машинна команда с подробно описание на

всяко от полетата, елементи на структурата. Младшите 6 бита в повечето случаи

съдържат ефективен адрес или регистрови адреси, което означава, че в основната

си реализация командната система разчита на формата

"регистър-регистър". В таблица 5.1.1.5 са посочени 16-те типа машинни

команди на този процесор.

Tаблица 5.1.1.5 Типове машинни команди в процесор МС680ХХ

|

№ |

b15b14b13b12 |

Команди за операции |

|

1 |

0 0

0 0 |

Команди с непосредствена адресация, за работа с

битове, MOVEP. |

|

2 |

0 0

0 1 |

MOVE.B,

прехвърляне на байт. |

|

3 |

0 0

1 0 |

MOVE.L

прехвърляне на двойна дума. |

|

4 |

0 0

1 1 |

MOVE.W

прехвърляне на дума. |

|

5 |

0 1

0 0 |

Разни (деление, умножение,

разширение, смяна на знака, тестване, NOT,

и други). |

|

6 |

0 1

0 1 |

ADDQ, SUBQ, Scc, DBcc, TRAPcc,

условен капан, събиране и изваждане с непосредствени данни. |

|

7 |

0 1

1 0 |

Вcc, BSR, BRA, условни преходи. |

|

8 |

0 1

1 1 |

MOVEQ, прехвърляне на непосредствени данни. |

|

9 |

1 0

0 0 |

OR, DIV, SBCD, операция ИЛИ, деление, 2/10-но изваждане. |

|

10 |

1 0

0 1 |

SUB, SUBX, изваждане, изваждане със заем от Х. |

|

11 |

1 0

1 0 |

Резервирано |

|

12 |

1 0

1 1 |

CMP, EOR, сравнение, сума по модул 2. |

|

13 |

1 1

0 0 |

AND, MUL, ABCD, EXG, операция И, умножение,

2/10-но събиране. |

|

14 |

1 1

0 1 |

ADD, ADDX,

събиране регистрово и с отчитане на пренос в Х. |

|

15 |

1 1

1 0 |

Изместване, ротация, операции с битови полета. |

|

16 |

1 1

1 1 |

Връзка с копроцесор. |

В операционната част на командата, чрез полетата в младшите 6 бита (вижте рисунката по-горе) могат да бъдат зададени различните схеми за формиране на изпълнителния адрес – таблица 5.1.1.6.

Tаблица 5.1.1.6 Кодиране на адресното поле в процесор МС68000

|

Метод за адресиране |

mod |

reg |

|

Непосредствено, даннов регистър |

0 0 0 |

№ на регистър |

|

Непосредствено, адресен регистър |

0 0 1 |

№ на регистър |

|

Косвен регистров |

0 1 0 |

№ на регистър |

|

Автоинкрементен |

0 1 1 |

№ на регистър |

|

Автодекрементен |

1 0 0 |

№ на регистър |

|

Базово индексен |

1 0 1 |

№ на регистър |

|

Индексен |

1 1 0 |

№ на регистър |

|

Пряк скъсен |

1 1 1 |

0 0 0 |

|

Пряк пълен |

1 1 1 |

0 0 1 |

|

Базово относителен |

1 1 1 |

0 1 0 |

|

Относителен |

1 1 1 |

0 1 1 |

|

Непосредствен |

1 1 1 |

1 0 0 |

3. Едночипови

микроконтролери

Като противоположност на процесорите със сложна архитектура и с общо предназначение, за които стана дума по-горе, тук ще се спрем на два широко разпространени и осветлени в литературата 8-битови микроконтролера. Архитектурата на тези процесори е значително по-тривиална, свързана със специфичното им промишлено приложение.

A) Едночипов микроконтролер PIC16Fxx

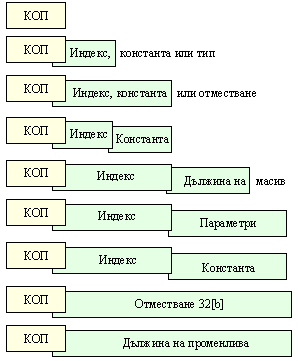

В системата от машинни команди на този процесор се съдържат само 35 команди. Всички команди имат една и съща дължина от 14 бита и се изтеглят от оперативната памет за един такт, тъй като данновата шина на паметта за команди (програми) е също 14-битова. Командите са класифицирани в три групи:

· Байтово-ориентирани команди – 18 на брой. Структурата на тези команди има вида, показан на фигура 5.1.1.3.

![]()

Фиг. 5.1.1.3. Структура на байтово-ориентирани команди

(PIC16Fxx)

Всички команди от тази група имат 6-битов

КОП (Opcode=00 хххх),

като всички комбинации съдържат в двата най-старши бита нули (00). Комбинациите

(00 0000) и (00 0001) са използвани по два пъти и се

декодират допълнително чрез бит b7. В

адресната част се съдържат два структурни елемента, които се използват по

следния начин:

- ако в 7-ми бит d=0 , тогава се използва регистър W ;

- ако в

7-ми бит d=1 , тогава

се използва регистър с номер #reg, посочен в

младшото поле.

· Битово-ориентирани команди – 4 на брой. Структурата на тези команди има вида, показан на фигура 5.1.1.4.

![]()

Фиг. 5.1.1.4. Структура на битово-ориентирани команди (PIC16Fxx)

Всички

команди от тази група имат 4-битов КОП (01 хх),

като всички комбинации съдържат в двата най-старши бита комбинацията (01). В

адресната част се съдържат два структурни елемента, които определят номера на

обработвания бит (#bit) и номера

на използвания регистър (#reg).

· Литерални и управляващи команди – останалите 13 на брой команди. Структурата на тези команди има вида, показан на фигура 5.1.1.5.

![]()

Фиг. 5.1.1.5.

Структура на литерални и управляващи команди (PIC16Fxx)

Както се

вижда, командите, които работят с 8-битов литерал, имат 6-битов КОП, а тези,

които работят с 11-битов литерал – 3-битов КОП. В адресната част на тези

команди се съдържа непосредствен операнд (стойност).

В заключение можем да отбележим, че този

процесор има изключително опростена структура на машинната команда, респективно

на полето КОП. Голяма част от възможните за КОП комбинации не са използвани.

Това е позволило на конструкторите да изберат и да използват тези комбинации,

които максимално биха улеснили тяхното декодиране.

Б) Едночипов микроконтролер АТ89Cxxx

За разлика от току що описания, за кода на операцията на 8-битовия микроконтролер АТ89Сххх е отделен винаги точно един байт. При това са оползотворени всичките 256 възможни комбинации на този байт, т.е. микроконтролерът има пълното 8-битово множество от 256 машинни команди. Командите са с променлив формат и имат дължина от 1, 2 или 3 байта. Кодът на операцията е хомогенен и не може да се интерпретира по друг начин освен в състава на пълната таблица от възможни комбинации. Как са подбрани комбинациите (с други думи КОП) на отделните команди и вложен ли е някакъв смисъл в това, е известно само на конструкторите на този процесор. В техническата документация на този процесор се предлага описание на структурата на всяка отделна машинна команда. Това, което тук можем да кажем е, че машинният език, респективно асемблерът за този процесор е значително по-труден за усвояване, главно поради големия брой команди.

4. Виртуални

процесори

Веднага

ще отбележим, че виртуалните процесори и свързаните с тях теми, съществено

излизат извън рамките на нашите интереси в тази книга. В същото време не можем

да не ги засегнем, защото те се подчиняват по свой начин на всичко казано в

предходните пунктове. С това искаме да уверим читателя в разбирането, че

основата на всички абстракции, които може да се сътвори Програмистът, стои

физическият процесор и всяка програма, която ще го наподобява, е неразривно

свързана с него.

Самото

наименование означава, че всеки виртуален процесор представлява своеобразен

програмен модел или цялостна програмна система, която емулира върху физическия

процесор друг, определен като виртуален, т.е. нереален, не съществуващ

физически. Малко по-високо стои понятието виртуална машина.

Към момента се използват две виртуални програмни платформи:

Най-общо те се състоят от:

·

Виртуален процесор ;

·

Боклукчия (Garbage

Collector). Задачата

му е да освобождава паметта, която са заемали вече ненужните обекти ;

·

Системи за защита, за идентификация и за оторизация

при изпълнение на виртуален код ;

·

Система за динамично управление кода (Reflection) ;

·

Базови библиотеки .

Предлагат се виртуални машини за различни

програмни езици. След създаване на първичния програмен код същият се компилира

до виртуален (Managed) код. Последният се нарича “байт-код” за Java-платформата или MSIL (Microsoft

Standard Intermediate Language) за .Net-платформата. За да се изпълни

виртуалният код, той трябва да се сведе (компилира) до native-код (машинен код за физическия процесор, на който работи

виртуалната машина). Има два подхода за свеждане до native-код

(осъществени от виртуалния процесор):

·

Чрез компилация по време на изпълнение ;

·

Чрез предварителна компилация до native-код

.

Ще

се спрем на първата виртуална платформа. Развитието на глобалната мрежа (Internet) и World Wide Web е причина за появата в средата на 90-те години на миналия век

на езици за програмиране, осигуряващи разпространение и разпределена обработка

на програми. Даваме този пример със съзнанието за актуалност и перспективност

на тази идея, подкрепяна от компании

като Hewlett-Packard (HP), IBM,

Sun Microsystems. Идеята се състои в доставка върху всяка реална

платформа на независимо от нея универсално изчислително средство за изпълнение

на доставения по мрежата програмен код. Така се появява езикът JAVA и реализиращата го виртуална JAVA-машина (JVM).

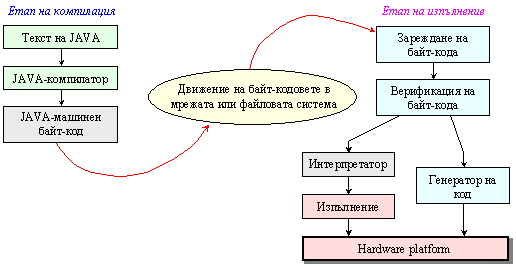

Както вече пояснихме, понятието виртуална машина

читателят следва да разбира като програмна

реализация на машинен модел. С други думи, конструираната JAVA-машина, не е реална (физическа), а съществува върху

реалната компютърна система във вид на програма. Една обобщена представа за

тази технология е представена на фигура 5.1.1.6.

Фиг. 5.1.1.6. Технологичен цикъл за обработка на Java-програми

Без да коментираме структурата и

възможностите на виртуалния процесор, тъй като това излиза извън нашите задачи

тук, във връзка с темата, която изясняваме като пореден пример, ще поясним

структурата на JAVA-машинните

команди. Тези команди имат дължина от 1 до 5 байта.

Фиг. 5.1.1.7. Структура и формат на JAVA-командите

Основната част от командите са еднобайтови. Кодът на операцията във всички случаи заема един байт. Останалите байтове (ако съществуват) се отнасят до адресната част на командите.

Към

настоящия момент понятието виртуална машина е значително обогатено.

Виртуализацията вече е доказала се софтуерна технология, която позволява върху

една конкретна хардуерна платформа да бъдат стартирани няколко виртуални

машини, които споделят ресурсите на физическия

компютър в множество среди. Различните

виртуални машини могат да работят под различни операционни системи и множество

приложения на един и същи физически компютър.

Виртуализацията е технология за поддръжка на изпълнението на

компютърен програмен код, от приложения към цели операционни системи, в

софтуерно контролирана среда. Такава среда от виртуални машини (VM`s) използва

наличните системни ресурси (памет, процесорно ядро, I/O-устройства и пр.) като ги

представя по такъв начин, че "гост"-операционните системи не могат да

разграничат виртуално базирана машина от физическа такава. В основата на тези

възможности стои така наречения Common Language Runtime (CLR), като

представлява среда за контролирано изпълнение на управляван код (своеобразна

виртуална машина). CLR-средата е онази част от .NET Framework на съвременните

платформи за програмиране, която може да изпълнява компилираните до нея .NET

програми в специална изолирана среда. Така CLR представляваща виртуална машина,

изпълнява командите на компилираните в езика Intermediate Language (IL)

програми. Езикът IL е междинен език, до който се компилират програмите от

всякакви .NET езици.

Технологията

Java Virtual Machine е различна от технологията .NET CLR, въпреки, че

двете технологии са сходни. По предназначение и двете са предназначени да

изпълняват програмен код за някакъв виртуален процесор. Този програмен код за

първата технология се нарича Java Bytecode, а за втората – IL-код.

Приема се, че IL-езикът е език от по-високо ниво, което позволява от него да се

компилира по-ефективно в сравнение с Bytecode.

Заключение

В заключение ще отбележим, че дадените примери подкрепят твърдението, че според структурирането на операционната част на командите, могат да се отделят два вида системи машинни команди:

·

Командни системи с неструктурирана операционна

част – хомогенен КОП. Кодът на операцията в такива системи обикновено за всички

команди е с една и съща дължина. Такива командни системи се наричат канонични . Обикновено такива са командните

системи в облекчени процесорни архитектури;

·

Командни системи със структурирана операционна

част – КОП в командите на такива системи представлява набор (постоянен или

променлив) от спецификатори. В тези случаи командната система е силно развита и

много богата, тъй като най-често обслужва сложна процесорна архитектура. Такива

командни системи се наричат ортогонални.

Както бе

посочено, броят на командите в даден процесор, може да бъде достатъчно голям. При това всяка

отделна операция има множество варианти, осигурени чрез съвкупност от машинни

команди, за които същинската операция, е една и съща. Така например тази

операция може да бъде събиране – събиране на числа без знак, събиране на

8-битови числа със знак, на 16-битови със знак, на 32-битови със знак и прочие.

Фактическите варианти са много и за всеки от тях има отделен двоичен код на

операцията. В резултат на това положение работата на програмиста с машинните

кодове е явно затруднителна. Ето защо за да се облекчи изучаването на системата

машинни команди и технологията на програмиране в системата на даден процесор,

кодът на операцията на машинните команди обикновено се изобразява в

предварителния текст на програмите не фактически (чрез двоичната си

комбинация), а чрез така наречения мнемоничен код – съчетание от букви (най-често части от думи), явно

подсказващи същинската операция. Така например, за операция събиране

обикновено се употребява мнемониката ADD (addition

- събиране), а за

изваждане – мнемониката SUB (subtraction

- изваждане). По-горе, в аванс, ние вече се възползвахме от този вид

представяне на някои машинни команди.

Представянето

на програмните текстове в машинен код, както вече отбелязахме, е крайно

нечетливо и трудно разбираемо, ето защо, освен кода на операцията, мнемонично

се представя и цялата структура на командата. Така текстовете на

мнемоничните машинни програми стават значително по-четливи и лесно

по-разбираеми. Правилата, по които се изразяват мнемонично машинните команди, а

от там целите програми, а така също и някои допълнителни правила, свързани

например със задачата за разпределение на адресното пространство на процесора

за нуждите на програмата, както и някои други, формират така наречения асемблерен език. Машинните програми се

съставят и представят от програмиста на асемблерен език, но съществуват в

оперативната памет и се изпълняват на фактическия машинен език. Преобразуването

(транслирането или още компилирането) на асемблерския текст на една програма в

машинен код се извършва автоматично от друга специална програма. Проблемите на

транслирането на приложните програми, както и проблемите им свързани с

операционната система, не са обект на нашето внимание и няма да бъдат

коментирани тук.

Следващият

раздел е:

5.1.2 Структура на

адресната част на машинната команда