Последната

актуализация

на този

раздел е от 2020

година.

5.5.1

Входно-изходни

операции

Под входно-изходни операции (или още въвеждане-извеждане) най-общо се разбира процесът по пренасяне на данни от външно устройство (ВУ) в оперативната памет на процесора или обратното. Този процес е много сложен, той е йерархичен и на всяко ниво има специфична организация. Пълното му изучаване значително би отклонило читателя от поставената тук цел, ето защо изложението на поставената тема ще бъде ограничено чрез съответната постановка на гледната ни точка. Както вече казахме в предидущия пункт, същността на тази постановка се състои в изясняване на основните подходи за реализация на входно-изходните операции в качеството им на изпълними операции, т.е. от гледна точка на процесора и на системата машинни команди.

Че процесът въвеждане например, е сложен структурен процес и че неговата реализация изисква значителни апаратни и програмни средства, може съвсем кратко да се покаже със следния пример. Нека една програма има необходимост от стойност за дадена променлива, която потребителят следва да зададе по време на нейната работа от клавиатурата, в качеството й на подходящото за целта външно устройство. Когато настъпи необходимият момент, той трябва да набере цифрите на числото чрез натискане на съответните клавиши. За целта последователността от клавишни (символни) кодове трябва да се възприеме, да се визуализира, да се преобразува от 2/10-чно в двоично число, при това да се представи в необходимата форма, формат и машинен код и едва тогава може да се запише в клетката от паметта, предназначена за съответната променлива, като нейна стойност. Читателят навярно разбира, след като вече се е запознал с глава 3, че процесът въвеждане, а така също и извеждане (в най-общото им разбиране) не може да се определи като изпълнима операция, тъй като по същество той се осигурява от цяло множество такива.

Верни на определената за нас гледна точка, вниманието ни тук ще бъде насочено непосредствено към онзи момент, в който поредната порция данни трябва при въвеждане да попадне в клетката от паметта, или когато при извеждане, трябва от клетката да бъде подадена към външния приемник. Точно в този момент, процесорът изпълнява някаква операция, свързваща "приемника" с "предавателя", която по същество тук ще се нарича входно-изходна операция (Op. I/O). Ако така се разбира входно-изходната операция, то едната страна в двойката (предавател-приемник) винаги ще бъде клетка в основната памет (или регистър от регистровата памет), а от другата страна ще бъде буферен регистър в логическата структура на външно устройство.

Казаното е достатъчно за да приемем, че процесорът “вижда” елементите на входно-изходната система не непосредствено, а като клетки в своето адресно пространство. Съвкупността от тези клетки (адреси), зад които се крие дадено външно устройство, се нарича проекция на външното устройство. С други думи, връзката между процесора и външното устройство, е проективна и се реализира чрез системната шина. Тъй като с клетките на проекцията на външното устройство процесорът ще може да оперира, като изпълнява в тях основните операции, характерни за едно запомнящо устройство, а именно четене и запис, то наборът от клетки, т.е. проекцията на външното устройство, ще наричаме програмен модел на външното устройство.

Клетката, до която процесорът има програмен достъп при входно-изходна операция, е прието да се нарича порт за вход-изход. Това наименование следва да се разбира буквално, тъй като входно-изходните операции (или още дейности) се схващат в компютърния жаргон като товаро-разтоварни относно програмата, за която са предназначени. В този смисъл, мястото през което преминават данните, е оприличено на пристанище (порт). Портът може да се разбира още като буферен регистър. Портът може да бъде достъпен както за четене, така и за запис, или само за четене и само за запис. Така всяко външно устройство от входно-изходната система представлява за процесора съвкупност от няколко порта, която нарекохме програмен модел на външното устройство.

В процеса на въвеждане-извеждане между процесора и системата за вход-изход се предават главно два вида данни - единият вид е предназначен и необходим за управление на процеса, а другият вид по същество представлява самите данни.

Управляващите данни, които изпраща (извежда) процесорът към системата за вход-изход, се използуват за инициализация на желания режим за работа, а управляващите данни, които процесорът прочита (въвежда) от системата за вход-изход, обикновено представляват някаква дума за състоянието на външното устройство.

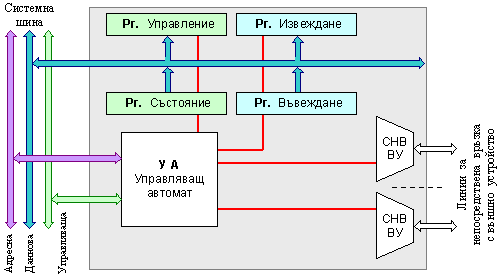

По силата на това разбиране и в съответствие с гледната ни точка, всяко външно устройство може да се изрази чрез общия програмен модел, показан на фигура 5.5.1.1.

Фиг. 5.5.1.1. Обобщен програмен модел на външно устройство

Представената структура може да бъде коментирана по следния начин: първото нещо, което се забелязва е, че тя е снабдена с два вида интерфейсни връзки (по-късно тук понятието интерфейс ще бъде специално и точно определено). Отляво е представена интерфейсната връзка със системната шина, а отдясно – физическия интерфейс с външното(-ните) устройство(-ва), в състава на който влизат схемите за непосредствена връзка с външното устройство (СНВВУ). От последното се разбира, че външното устройство най-често не може да бъде подключено непосредствено към системната шина. Това става чрез посредник, който се нарича контролер или още адаптер. Контролерът за вход-изход, като елемент в структурата на изчислителната система, обикновено се проектира и реализира така, че да бъде в състояние да управлява повече от едно външно устройство, разбира се от един и същи вид.

Функции

на

входно-изходните

контролери

И така, ще се спрем малко по-подробно на входно-изходните контролери. Такъв контролер отговаря за управлението на присъединените към него едно или няколко ВУ, както и за данновия обмен с това ВУ от една страна, и с основната памет или с регистрите на процесора – от друга страна. Основните функции на контролера за вход-изход (КВ/И) може да формулираме както следва:

· Локализиране на данните върху носителя ;

· Управление и синхронизация на процесите ;

· Обмен на данни ;

· Буферизация на данните ;

· Откриване и идентификация на грешки.

Локализиране

на данните

Под локализиране се разбира възможността за обръщение към дадено ВУ и последващата адресация на данните в него. Адресът на ВУ обикновено е указан в адресната част на машинната команда за вход-изход. Както тук по-късно ще бъде подробно коментирано, в състава на системата за вход-изход могат да влизат няколко КВ/И. Към всеки контролер могат да бъдат подключени по няколко ВУ,ето защо на всеки контролер е разпределена определена част от адресното В/И пространство, независимо дали това пространство е единно или е разделно (което ще бъде пояснено по-долу). Старшите разряди на адреса обезпечават избора на конкретния контролер в системата за вход-изход. Младшите разряди представляват уникалния адрес на регистрите в контролера или подключените към него ВУ.

Една от функциите на КВ/И трябва да извърши проверка за съответствието (за принадлежността) на постъпилият адрес към разпределената за контролера адресна област. Ако съответствието се потвърди, контролерът следва да осигури декодиране на постъпилия адрес и да отправи данните към адресирания обект или обратно.

За простите ВУ (клавиатура, принтер и пр.) адресът на ВУ еднозначно определя и разположението на данните в това устройство. По-сложните ВУ тази информация изисква допълнителна детайлизация. Така например, за ЗУ на магнитен диск следва да се укаже номер на цилиндър, номер на сектор и пр. Тази част от информацията за адреса се предава в контролера не по адресната шина, а във вид на служебни съобщения, които се препращат по данновата шина. Обработката на тази информация в контролера е значително по-сложно по сравнение с избора на определен регистър във ВУ. В частност, тя може да изисква от контролера определена процедура за търсене на информация върху носителя на данни.

Управление

и

синхронизация

КВ/И трябва да контролира преместването на данните между вътрешните ресурси на изчислителната система и периферните устройства. При това следва да се отчитат множество фактори. Преди всичко следва да се вземе под внимание факта, че процесорът може да взаимодейства едновременно с няколко ВУ, при което бързодействието на присъединените устройства може да варира в широки граници – от няколко байта в секунда в терминалите, до десетки милиони байтове при обмен с дисковете. Ако в системата се използват шини, всяко взаимодействие между процесора и контролера включва едно или няколко арбитражни процедури.

За разлика от обмена с паметта, входно-изходните процеси и тези в централния процесор протичат не синхронно. Поредната порция данни може да бъде предадена в устройството едва тогава, когато то потвърди своята готовност за това. Аналогично, въвеждането на данни е допустимо само ако те са достъпни в устройството. Несинхронният характер на В/И-те процеси предполага обмен на специални сигнали (при операция извеждане например):

1. Процесорът с помощта на сигнал от типа “данните са достоверни” (ДД=1) съобщава на устройството за достъпността на данните върху изходната му шина ;

2. След приемането на данните, извеждащото устройство изпраща към процесора обратен сигнал, потвърждаващ успешното приемане на данните в устройството (ДП=1) ;

3. След като получи очакваното потвърждение, процесорът сваля сигнал ДД и подготвя нова порция данни върху изходната шина ;

4. Откривайки, че сигналът ДД е неактивен (ДД=0) устройството на свой ред сваля потвърждаващия сигнал (ДП=0), след което е готово за приемане на новата порция данни, очаквайки процесорът да вдигне сигнал ДД=1.

Става ясно, че КВ/И е длъжен да оповестява процесора за своята готовност за обмен, а така също да подготвя и съдържа оперативна информация за събитията, настъпващи в системата за В/И.

Обмен

на

информация

Функцията, осигуряваща обмена на данни, е основна. От страна на "големия интерфейс", това е обменът с централния процесор, а от страна на "малкия интерфейс", това е обмена с ВУ. В този план изискванията към контролера (КВ/И) диктуват последователност от действия, които изпълнява процесорът:

1.

Избира

необходимото

външно

устройство ;

2.

Определя

състоянията

на

контролера и

на външното

устройство ;

3.

Изпраща

към

контролера

указания за

подключване

на

необходимото

ВУ ;

4.

Получава

от КВ/И

потвърждение

за подключване

на

поисканото

ВУ ;

5.

Разпознава

сигнала за

готовност на

ВУ да предаде

поредната

порция данни

;

6.

Приема

(предава)

порцията

данни ;

7.

Изпълнява

циклическо

повторение

на предходните

два пункта,

до

завършване

на трансфера

в пълния му

обем ;

8.

Изпълнява

логическо

отключване

на ВУ от процесора.

Функцията “обмен” с централния процесор включва още:

· Разпознаване на команди: контролерът получава команди от процесора, които са във вид на сигнали или комбинация от такива, по системната управляваща шина ;

· Трансфер на данни между контролера и процесора ;

· Известяване за състоянието: по причина на бавното функциониране на ВУ е важно да се знае състоянието на КВ/И. Например, в момент на получаване на заявката за препращане на данни в процесора контролерът може да не бъде готов да изпълни този трансфер, ако още не е завършил предходната команда. Този факт следва да бъде съобщен на процесора чрез съответния сигнал. Възможни са още и сигнали, съобщаващи за възникване на грешки ;

· Разпознаване на адрес: контролерът е длъжен да разпознава адреса на всяко ВУ, което той управлява.

Освен обмена с процесора, контролерът трябва да осигури и функцията “обмен” с ВУ. Този обмен също включва предаване на данни, команди и информация за състоянието.

Буферизация

Като правило всички ВУ изостават със скоростите на обмен спрямо процесора и паметта. Основният подход за компенсиране на тези различия е буферизацията. При извеждане към външно устройство данните се изпращат от основната памет към контролера с голяма скорост, където се записват в буфер, а в последствие се изпращат към ВУ със скорост, която му съответства. При обратната операция (въвеждане) също се буферизират за да не се заставя паметта да работи в режим на бавен обмен. Ясно е, че КВ/И следва да обезпечава съответните скорости за трансфер в качеството си на посредник между две системи, съответно подключени към “малкия" и към "големия" интерфейси.

Откриване

на грешки

Процесорът следва да съобщава за всяка грешка, настъпила в процеса на обмен. Грешките могат да бъдат причинени от най-разнообразни фактори:

· Замърсяване и влага ;

· Несъответстваща температура на обкръжаващата среда ;

· Електромагнитно облъчване ;

· Подскоци в захранващото напрежение ;

· Остаряване на елементната база ;

· Грешки в системното програмно осигуряване ;

· Грешки в потребителското програмно осигуряване.

Степента на влияние на всеки от горните фактори зависи от типа и конструкцията на КВ/И и ВУ. Например, на замърсяване са чувствителни оптическите и механичните елементи, а температурните колебания влияят на електронните елементи, на които влияе още и електромагнитното излъчване. Нестабилното захранващо напрежение може да повреди или изкриви работата на електронните схеми като цяло.

Стареенето като фактор е характерен както за механични така и за електронни елементи. В механичните елементи той се изразява във вид на износване, причиняващо изменения в позиционирането на датчици, четящи или записващи глави, ограничители и пр. Стареенето на електронните елементи причинява изменения в електрическите параметри на електронните схеми, в резултат на което могат да се променят формата, продължителността, нивата, синхронноста между отделните сигнали.

Грешките от несъвършено програмно осигуряване могат да бъдат:

· Непредвидени последователности от команди или от кодови комбинации ;

· Некоректно разпределение на паметта ;

· Недостатъчен обем на буфера за В/И ;

· Необмислени и непроверени комбинации от системни модули.

Потребителското програмно осигуряване най-често генерира грешки при:

· Нарушена последователност при изпълнение на програмата ;

· Некоректни процедури.

Обобщена

логическа

структура на

входно-изходния

контролер

Логическата структура на КВ/И зависи от броя и от сложността на ВУ, които той ще управлява, но тя може да бъде представена най-общо както следва.

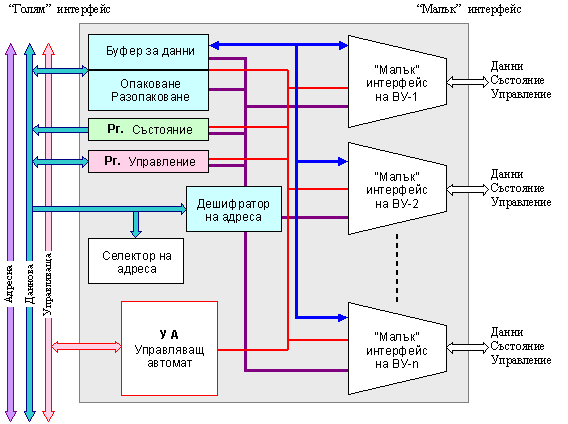

Фиг. 5.5.1.2. Обобщена структура на контролер за В/И операции

Връзката между контролера за вход-изход и ядрото на процесора се осъществява чрез системната или чрез специализирана шина (така наречения "голям” интерфейс). Големите различия в архитектурата на системата машинни команди и на шините в изчислителните системи е причина трудно да бъдат унифицирани контролерите за вход-изход от към страната на големия интерфейс. Това е причината даден КВ/И, който е създаден за определена платформа, да не може да бъде подключен към друга.

Данните, които се предават по "големия" интерфейс, се буферират в буфера за данни, с което се компенсират различията в бързодействието между ядрото и ВУ. Разрядността на регистъра за данни обикновено съвпада с ширината на свързващата шина (4 или 8 байта). В същото време повечето ВУ практикуват трансфер на байтове. За да се предават по широката шина на големия интерфейс, порцийките от малкия интерфейс се опаковат в специален възел. В обратната посока същият възел изпълнява разопаковане на дългата дума до ширината на шината към ВУ.

В регистъра за управление се записват изпратените от процесора команди. Съдържанието на този регистър не е хомогенно, то се дели на подполета и отделни битове със специфично предназначение. Типични команди са за нулиране на регистър, за ресет на ВУ, за запис, за четене и пр. Възможни са няколко управляващи регистъра (за контролера, за отделните устройства ).

Регистърът на състоянието съхранява думата на състоянието, която също не е хомогенна. Отделни нейни подполета и битове имат специфично предназначение. Типични състояния са свободен, зает, готов, неготов, зает, изключен и пр. Възможни са няколко подобни регистри.

Програмният достъп да отделните регистри се осигурява от проективната връзка на контролера в адресното пространство на процесора. Така достъпните регистри стават портове. Достъпността на адреса се контролира от вградения селектор, а дешифраторът разпознава конкретните регистри.

Цялостното управление на контролера е апаратно и се осигурява от управляващия автомат.

Контролер за вход-изход, който самостоятелно управлява ВУ и комуникира с процесора само с команди от високо ниво, обикновено се нарича канал за вход-изход.

Методите за управление на процесите при въвеждане и при извеждане на данни, ще бъдат обект на допълнително пояснение в следващи раздели.

Организация

на

проективната

връзка

Да се върнем на програмния модел на ВУ (което се отнася и за контролера като цяло). Всеки от четирите регистъра на програмния модел е достъпен за процесора. За целта тези регистри имат еднозначно определени адреси в адресното пространство на процесора, в които управляващият автомат (УА), с помощта на системните управляващи сигнали на съответните машинни команди, записва или чете данни.

В зависимост от особеностите на външното устройство, общият програмен модел може да бъде конкретизиран. Например, ако устройството е само за въвеждане (клавиатура), то в него регистърът за извеждане може да липсва. Ако пък устройството е само за извеждане (принтер), може да липсва регистърът за въвеждане. Много често в по-простите устройства регистърът за управление и регистърът на състоянието са обединени в един регистър, а в по-сложните е възможно отделянето в структурата и на други функционални регистри. С цел ускоряване на обмена, в контролерите на външните устройства се прилага механизмът за буфериране на данните. Входно-изходните регистри се заменят с FIFO-буфери, чийто обем и дисциплина за достъп е съобразен с конструкцията на устройството от една страна и ширината на шината – от друга страна. Дисковите запомнящи устройства, в които данновата организация на носителя е по блокове, предлагат възможност за обмен само по блокове. Обемът на блока е равен на обема на дисковия сектор, примерно 512 байта, ето защо буферите за данни в такива IDE/ATA контролери имат този обем. Режимът на блочен обмен се определя от факта, че ширината на данновата шина е по-малка от обема на блока, а веднъж започналият обмен не може да се спира – той завършва след предаване на всички порции, съставящи блока. В дисковите устройства буферите са еднопортови и двупортови. Във втория случай буферите могат да съвместяват достъпа от страна на двата интерфейса (вижте фигура 5.5.1.1), с което, разбира се, се постига по-висока производителност. Съвместеното използване на двата интерфейса най-често използва кръговия FIFO-буфер (вижте структурата от фигура 4.3.1 и следващите там пояснения), който позволява непрекъснат последователен обмен на повече от един блок. Съществуват външни устройства, в които се прилага пакетна организация на данновия поток. Пакетът се предава с определена скорост (10, 100, 1000[Mib/s] за три поколения Ethernet контролери) и следва да се приема със същата скорост, а това изисква буфериране. За 100 мегабитовите PCI контролери буферите са с обем от 64[B]. Почти във всички периферни контролери се използват различни комбинации от трите основни вида режими за обмен – регистров, блочен и пакетен.

И така, четирите порта на представения модел се разглеждат като клетки в адресното пространство на процесора. За изпълнение в тях на основните операции всяка програма трябва да употреби съответните машинни команди. В такива команди, освен кодът на операцията, трябва да се посочи адресът на предавателя и адресът на приемника и в този смисъл тяхната структура може да се определи като двуадресна. Машинните команди за реализация на входно-изходни операции се отделят и разглеждат в отделна група на командната система (вижте поясненията в §5.1).

На практика съществуват два подхода за непосредствената реализация на входно-изходните операции като изпълними. Ще припомним, че под изпълнима операция разбираме такава операция, която може да бъде заповядана с машинна команда. А подходите са:

1. Изпълнение на операциите в единното адресно пространство на основната памет;

2. Изпълнение на операциите в разделно адресно пространство.

Единно

адресно

пространство

В този случай входно-изходната система не се разпознава от процесора като такава. Тя може само да се интерпретира чрез своята проекция в общото адресно пространство. С други думи, на входно-изходните портове процесорът гледа като на клетки от оперативната памет и изпълнява в тях обичайните за оперативната памет операции четене и запис. От тук следва, че при такава интерпретация на входно-изходните портове на външното устройство, процесорът не се нуждае от допълнителни (специални) машинни команди, различни от тези за работа с оперативната памет. Обикновено това са команди от вида LOAD (четене на клетка от паметта и зареждане на регистър) и STORE (запис на съдържанието на регистър в клетка от паметта). Ако програмистът чете една машинна програма той не е в състояние да различи двойствената интерпретация на адресираната от командите LOAD или STORE клетка. За да може да направи това, следва да му е предварително известно разпределението на адресното пространство. Нещо повече, една и съща клетка в даден момент за някои команди от програмата би могла да бъде източник на данни или място за съхранение на междинни резултати. В други моменти тази клетка може да играе ролята на порт и нейното съдържание да се прехвърля във външно устройство или обратно, нейното съдържание да се обновява с данни, пристигащи от външно устройство. Разбира се, тази възможност би могла да създаде много сериозни неприятност, ето защо най-често се практикува правилото, че ако една клетка реализира входно-изходен порт, тя не бива и не може да се използва за други оперативни цели, т.е. за съхранение на команден код или на данни и междинни резултати. В повечето системи, осъществяващи входно-изходни операции в единното адресно пространство на процесора, същото е разделено на области – за оперативна работа и за вход-изход.

Може да се твърди, че липсата на специализирани машинни команди за входно-изходни операции в такива системи е достойнство, тъй като облекчава командната им система. В същото време обаче броят на адресите, които могат да бъдат резервирани за разполагане на входно-изходни портове, е неограничен. Освен това, тъй като наборът команди, които могат да работят с клетки от оперативната памет е сравнително многоброен, то следва, че същите команди могат да се използват и върху съдържанието на входно-изходните клетки. Но най-ценното е това, че при този подход значително се опростява системната шина на процесора. Този подход за реализация на входно-изходните операции обаче има и своите недостатъци, които се изявяват, когато трябва да се реализира богата и разнообразна входно-изходна система. Фактът, че тя се проектира в основното адресно пространство означава, че при разрастване тя би могла да попречи на оперативните функции на оперативната област от паметта, тъй като я ограничава по обем, а в някои случаи и я раздробява на няколко отделни области. Освен това този подход не е най-подходящият за реализиране на системата на унифицирания интерфейс, тъй като го усложнява, което може да доведе в крайна сметка до ниско бързодействие на входно-изходния процес като цяло.

Разделно

входно-изходно

адресно

пространство

Запазването на оперативното предназначение на адресното пространство на процесора е изискване важно за комфортните условия на виртуалната памет, на операционната система и свързаните с технологичните програмни среди средства. Не е приятно да делиш ресурсите си с някой друг. Наличието на области в оперативната памет с друго функционално предназначение създава неудобства. Ето защо към системната шина на процесора се създава огледално (отразено) или още изолирано адресно пространство, предназначено за функциите на входно-изходната система. Създаването на двойнствена интерпретация на адресното пространство се постига чрез разделяне на машинните команди на групи, такива, които “виждат” само предназначеното за тях пространство. За процесори, които използват този подход се казва, че имат изолирани адресни пространства – от една страна за оперативни и от друга страна за входно-изходни операции. Машинните команди, които виждат само входно-изходното адресно пространство, естествено са команди за въвеждане и извеждане и те са отделени в отделна група.

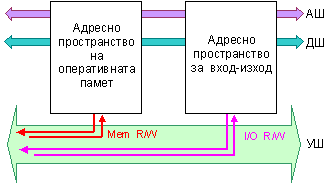

Фиг. 5.5.1.2. Представа за разделни (изолирани) адресни пространства

Фигурата изразява това, че адресната и данновата шини са общи и “пронизват” и двете пространства, но изборът на клетка или на порт осъществява управляващата шина с помощта на съответните управляващи сигнали.

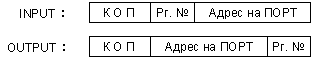

Командите “Въведи” (INPUT, или IN) и “Изведи” (OUTPUT, или OUT) правят входно-изходните операции изпълними. В архитектурата IA-32 тези команди имат още разновидностите INS, INSB, INSW, INSD за въвеждане на символи и съответно за извеждане OUTS, OUTSB, OUTSW и OUTSD. Алгоритмичната същност на тези команди обаче не се различава съществено от операциите "Четене" и "Запис" на командите за работа с оперативната памет. Типичната структура на командите за вход-изход в архитектурата IA-32 има вида:

Фиг. 5.5.1.3. Структура на машинните команди за вход-изход

Може да се каже, че по структура командите са двуадресни - единият адрес (Рг.№) представлява номер регистър от регистровата памет на процесора, а другият (Адрес на ПОРТ), е абсолютен (пряк) адрес на порт във входно/изходната памет на процесора. Специално трябва да отбележим, че при адресиране на клетка от оперативната памет, не се използват други методи за адресиране освен пряк. Това е така, защото програмните модели на различните външни устройства са твърдо разпределени (проектирани) във входно-изходното адресно пространство на процесора. Не е разрешено една програма или операционната система да премества даден порт от един в друг адрес.

За по-лесна реализация на адресните дешифратори и формиране на сигнали от типа Е (Enable) или CS (Chip Select), се избират адресите от началото на адресното пространство. В този смисъл някои автори пишат, че то има обем 64[KiB], тъй като полето “Адрес на ПОРТ” е 16 битово. В исторически план първоначално са използвани младшите 10 бита в адресното поле, в последствие младшите 12, а към настоящия момент младшите 16 бита от адреса. Това определя реално използваемо входно-изходно пространство в обем от 1[KiB], 4[KiB] и 64[KiB] съответно. На IBM дължим стандартизацията на разпределението на входно-изходното пространство за компютърните системи с архитектура IA-32, към която се придържат производителите на контролери и която привеждаме по-долу:

12-битов 16-чен адрес Предназначен за

000 ¸ 00F Контролер за ПДП №1 ;

010 ¸ 01F Разширение за КПДП №1 ;

020 ¸ 021 Програмируем контролер за прекъсване №1 ;

040 ¸ 05F Таймер ;

060 Диагностичен регистър POST (само запис) ;

061 Източници на NMI и управление на звука ;

060, 064 Контролер на клавиатура ;

070 ¸ 07F CMOS-памет и маска за NMI ;

080 ¸ 08F Регистри на страниците на КПДП ;

090 ¸ 097 PS/2-микроканал, Арбитър ;

0A0 ¸ 0BF Програмируем контролер за прекъсване №2 ;

0C0 ¸ 0DF Контролер за ПДП №2 ;

0F0 ¸ 0FF Копроцесор 80287 ;

100 ¸ 1EF PS/2-управление на микроканала ;

170 ¸ 177 Контролер на твърд диск №2 (IDE №2) ;

1F0 ¸ 1F7 Контролер на твърд диск №1 (IDE №1) ;

200 ¸ 207 Гейм-адаптер ;

238 ¸ 23F Порт СОМ4 ;

278 ¸ 27F Паралелен порт LPT2 ;

2C0 ¸ 2DF EGA №2 ;

2E0 ¸ 2E7 Порт СОМ4 ;

2E8 ¸ 2EF Порт СОМ4 ;

2F8 ¸ 2FF Порт СОМ2 ;

300 ¸ 31F Платка прототип ;

338 ¸ 33F Порт СОМ3 ;

370 ¸ 377 Флопи-контролер №2 ;

376 ¸ 377 Портове на команди за IDE №2 ;

378 ¸ 37F Паралелен порт LPT1 ;

380 ¸ 38F Синхронен адаптер SDLC/BSC №2 ;

3A0 ¸ 3AF Синхронен адаптер BSC №1 ;

3B0 ¸ 3BB Монохромен адаптер ;

3B4 ¸ 3C9 PS/2-видеосистема ;

3BC ¸ 3BF Паралелен порт LPT1 ;

3C0 ¸ 3CF EGA №1 ;

3C0 ¸ 3DF VGA ;

3D0 ¸ 3DF CGA ;

3E0 ¸ 3E7 Порт СОМ3 ;

3E8 ¸ 3EF Порт СОМ3 ;

3F0 ¸ 3F7 Флопи диск контролер №1 ;

3F6 ¸ 3F7 Портове на команди за IDE №1 ;

3F8 ¸ 3FF Порт СОМ1 .

Във файловата система /proc, файлът /proc/ioports съдържа сведения за адресите на входно-изходните портове. Ако се изпълни командата <cat /proc/ioports >, ще се получи листинг, подобен на показания по-долу:

Листинг 1. /proc/ioports

|

0000-001f : dma1 0020-003f : pic1 0040-005f : timer 0060-006f : keyboard 0070-007f : rtc 0080-008f : dma page reg 00a0-00bf : pic2 00c0-00df : dma2 00f0-00ff : fpu 0170-0177 : ide1 01f0-01f7 : ide0 02f8-02ff : serial(auto) 0376-0376 : ide1 0378-037a : parport0 03c0-03df : vga+ 03f6-03f6 : ide0 03f8-03ff : serial(auto) 0cf8-0cff : PCI conf1 1800-181f : Intel Corp. 82801DB USB (Hub #1) 1800-181f : usb-uhci 1820-183f : Intel Corp. 82801DB USB (Hub #2) 1820-183f : usb-uhci 1840-185f : Intel Corp. 82801DB USB (Hub #3) 1840-185f : usb-uhci 1860-186f : Intel Corp. 82801DB Ultra ATA Storage

Controller 1860-1867 : ide0 1868-186f : ide1 1880-189f : Intel Corp. 82801DB/DBM SMBus

Controller 18c0-18ff : Intel Corp. 82801DB AC'97 Audio

Controller 18c0-18ff : Intel

ICH4 1c00-1cff : Intel Corp. 82801DB AC'97 Audio

Controller 1c00-1cff : Intel

ICH4 2000-203f : Intel Corp. 82801BD PRO/100 VE (LOM)

Ethernet Controller 2000-203f : e100 |

Портовете се номерират от 16-те адреси, но могат да бъдат именовани с собствените си имена, като например: keyboard, timer, parallel (за принтер), serial (за модем), vga+ (видеокарта). Трябва да се отбележи, че например първият паралелен порт (parport0) притежава адресите в интервала 0378-037А, което е отразено на първия листинг, но стандарта LPT1 допуска да използва и адресите 0378-037F. Стандартното установяване на портовете ще ви даде следния листинг:

Листинг 2.

Стандартни

установки за

входно-изходни

портове

|

1FO-1F8 : Hard

Drive Controller, 16-bit ISA 200-20F :

Game Control 210 : Game I/O 220 : Soundcard 278-27F :

LPT2 2F8-2FF :

COM2 320-32F :

Hard Drive Controller, 8-bit ISA 378-37F :

LPT1 3B0-3BF :

Monochrome Graphics Adapter (MGA) 3D0-3DF :

Colour Graphics Adapter (CGA) 3F0-3F7 :

Floppy Controller 3F8-3FF :

COM1 |

Адресът и данните използват общите за адресните пространства шини, но входно-изходната операция се изпълнява в порт, под управлението на отделни управляващи сигнали. В този смисъл, при този подход, може да се каже, че процесорът вижда входно-изходната система през входно-изходното адресно пространство.

Процедурата за обръщение към входно-изходната памет, която се реализира от командите за вход-изход, се различава от тази, изпълнявана в оперативната памет само по това, че вместо сигналите MEM_READ и MEM_WRITE, тя генерира сигналите I/O_READ и I/O_WRITE. При така описаната постановка не е трудно да се разбере, че благодарение на "изолацията" на входно-изходното адресно пространство от това на оперативната памет, с един и същи адрес може да се получи достъп както до клетка от ОП, така и до порт за въвеждане или до порт за извеждане във входно-изходната памет. Това обаче става с различни команди - едните за работа с ОП, другите за работа с входно-изходната памет.

Когато към процесора са подключени няколко еднакви устройства за вход-изход, всяко от тях има свой собствен интерфейс. Апаратните средства на интерфейса са еднакви, а портовете имат различни адреси. Обменът с тези устройства обикновено се осъществява с помощта на една и съща драйверна програма, която всеки път трябва да работи с различни адреси. Тази програма за съвместно използване се разработва лесно, когато процесорът използва единно адресно пространство, където за машинните команди са достъпни различни методи за адресация. Когато обаче процесорът използва изолирано адресно пространство, разработването на драйвер за съвместно използуване е по-трудно, ето защо адресирането на портовете, както по-горе отбелязахме, обикновено е само пряко.

Типичната съвременна компютърна система има силно развита входно-изходна система, за която някои от изказаните по-горе положения се променят. Това се отнася най-вече до системата от връзки, която се характеризира с йерархичност, с различна производителност и с приложение на различни стандарти. Компютърната система може да разполага с няколко вида шини (шина на основната памет, шина PCIe, шина SCSI, шина USB и пр.). В условията на няколко входно-изходни шини се появява проблем с разпознаването на разделния адрес, който процесорът подава на системната шина. По тази причина в устройството за управление на паметта се добавят специални апаратни средства.

Някои от тези проблеми предстои да бъдат разгледани в следващите раздели.

Следващият

раздел е:

5.5.2 Организация

на входно-изходния

обмен