Последната актуализация на този раздел е от 2020 година.

5.5.3.2 Хъбова

архитектура на входно-изходната система. USB4

В края на 90-те години от минали век PCI шината има сериозни конкуренти. Високоскоростните режими на двуканалния IDE-контролер, в които се обслужват каналите с пряк достъп до паметта UltraDMA (АТА/100, АТА133), стават тежки за PCI-шината. Появяват се скоростните интерфейси Gigabit Ethernet, FireWire (100/200/400/800[Mib/s]), а така също USB 2.0 (480[Mib/s]), което е около 60[MiB/s]. Така, два скоростни диска и няколко устройства с интерфейс USB 2.0 натоварват системната шина с повече от 300[MiB/s]. Това е една производителност, която не е по силите на PCI-шината. Към тази констатация следва да добавим факта, че периферията на компютърните системи ставаше все по-разнообразна. На тази шина се подключваха мрежови карти, контролери IEEE 1394 (FireWare), SATA RAID (redundant array of independent disks – масив от независими дискове). Дълго време контролерите RAID съществуваха като отделни карти за разширение. В последствие производителите на сървърни системи започнаха да ги вграждат върху дънните платки. Така в наследство всички съвременни южни мостове съдържат такива контролери. Тези устройства съдържат в себе си необходимия контролер и необходимите обвързващи схеми и се подключваха чрез PCI-слотовете, когато интегрираните на дънната платка интерфейси не достигаха. Освен това много от устройствата са в по няколко екземпляра. Чрез периферните шини могат освен това да бъдат подключвани и по-сложни устройства, каквито са звуковите карти, TV-тунерите и TV-декодери, цифровите анализатори, секюрити преобразователи и различни уникални системи, свързани с конкретни приложения на компютърната система, разработвани от потребителя. Освен това винаги е било необходимо към системата да се подключват и бавнодействащи устройства, такива като клавиатури, мишки, фотоапарати, скенери, цифрови телефони, flash-устройства и пр. Към всичко това следва да добавим и желанието на потребителя да прави промени в конфигурацията на системата си без нейното изключване или с други думи прилагане на технологията plug-in-play (вижте поясненията в пункт 5.4.2) в пълна степен. Всички тези устройства по някакъв начин получават данни от системата или ѝ доставят такива. До излизането на пазара на чипсетите i915X и i925X в качеството на периферни шини продължава да се използва непроменената PCI-шина. След появата на тази шина (през 1992 година) процесорната, графическата, междумостовата и шината на паметта непрекъснато се модернизираха, а PCI-шината, заради желанието да се запази съвместимостта с огромния брой произведени за нея устройства, оставаше непроменена.

Това състояние не можеше да продължава дълго и то доведе до търсенето на универсален начин за свързване на подобно множество от устройства. Разработена беше шината USB (Universal Serial Bus) – универсална последователна (серийна) шина, която в голяма степен определя архитектурата на входно-изходната система. Пълното описание на USB интерфейса не можем да си позволим тук – документацията му е повече от 1000 страници. С нея читателят може да се запознае като посети следните адреси:

https://en.wikipedia.org/wiki/USB

;

https://www.usb.org/documents

.

Тук по-долу ние ще изложим само основните разбирания и понятия.

Тъй като USB шината е само с една информационна проводна двойка, то предаването на данните е последователно (бит след бит във времето). Предаването на данни на по-голямо разстояние (включително извън физическата компютърна система) е свързано с многократното й ретранслиране с цел възстановяване на амплитудите и времевите характеристики на полезния сигнал. Това налага сигналът да се предава не в истинния си вид, а в кодиран вид. Кодовете, които се използват за представяне на сигнала при неговото последователно предаване се наричат линейни кодове. Най-простият униполярен линеен код се нарича NRZ (Non Return to Zero). Същността на кода се състои в наличието или отсъствието на импулси в моментите, маркирани от тактовите импулси. Така нулата се кодира с липса на импулс (ниско ниво), а единицата с наличие на импулс (високо ниво) в моментите на тактовите синхронизиращи импулси. Този код има редица недостатъци, които тук няма да коментираме, ето защо той се прилага във вид на биполярен сигнал. Биполярният сигнал се образува от елементи с два диференциални сигнала (вижте фигура 5.5.3.1.10) и се разпространява чрез усукана двойка проводници с обща екранировка. Разработени са и други линейни кодове. Едни от най-известните линейни кодове се характеризират като кодове с излишък. Техен основен представител е кодът, наречен “Манчестер-II”. Кодовете с излишък отстраняват почти всички недостатъци на линейните кодове. Излишъкът в кода може да се реализира в различен смисъл. В кода “Манчестер-II” той е реализиран чрез предварителен (подготвителен) преход на сигнала в състояние нула. Друг смисъл в излишъка се състои във въвеждане на трети електрически потенциал във формата на сигнала, например биполярна форма със средно положение (средна стойност). Основният представител на методите за кодиране с този вид излишък се нарича AMI (Alternate Mark Inversion). За повече подробности по въпросa за кодиране на последователно предавана информация отправяме читателя към специализираната литература.

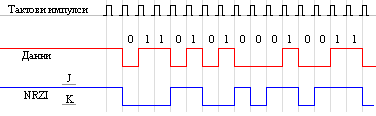

Методът, който е избран за кодиране на битовете в технологията USB се нарича NRZI (Non Return to Zero – Inverted) “Код без връщане към нулата – инвертиран”. Става дума за сигнал с две нива, т.е. за биполярен сигнал предаван по диференциална усукана двойка проводници. Същността на това кодиране е илюстрирана на следващата фигура.

Фиг. 5.5.3.2.1. Кодиране по метода NRZI

Както се вижда, входната последователност от битове се превръща в друга последователност по силата на следното правило: сигналът сменя нивото си в началото на всяка нула. Началото на всеки бит се приема през равномерна стъпка.

Основното звено в структурата на USB шината се нарича хъб (Hub – център, концентратор). При разработването на концепцията за тази шина се цели ниска цена, гъвкавост и широк диапазон на пропускателни възможности (от бавни до бързи), отдалеченост на подключваните устройства, както и динамичен състав. За адресиране на устройства е заделено 7-битово поле и максималният брой устройства е 127. Така компромисният вариант води до избор на последователен формат на данните по време на трансфер. Синхронизацията и данните се кодират и предават съвместно. При тази първоначална уговорка по-нататък няма никакви ограничения в преследването на високите скорости или на по-големите разстояния. USB-кабелът съдържа 4 проводника: 2 за предаване на потенциала на данновия сигнал (усукана двойка +D и -D), един неутрален GND (ground) и един положителен силов Vcc. Съединителното гнездо от към по-високото ниво се нарича А-щекер (женски), а съединителя от към по-ниското ниво – В-щекер (мъжки). Съществуват и разновидности, като например mini-В-щекери за присъединяване на цифрови фотоапарати, мобилни комуникационни устройства и др. В зависимост от консумацията USB-устройствата и хъбовете могат да получават захранване по шината и от автономен захранващ източник. До настоящия момент са специфицирани три скорости за USB-трансфер: за USB 1.0 до 1,55[Mib/s], за USB 1.1 до 12[Mib/s] и за USB 2.0 до 480[Mib/s]. Този параметър е в непрекъснато повишаване. Към момента (2008 година), в който излезе първия печатен вариант на тази книга, беше публикуван стандартът USB 3.0, който гарантираше скорост на трансфера от порядъка на 5[Gib/s] или още 500[MiB/s], т.е. повишение с цял порядък. Този стандарт беше доразвиван и актуализиран два пъти. Вариантите USB 3.1 и USB 3.2 гарантираха скорости от порядъка на 10[Gib/s] и 20[Gib/s] съответно.

Архитектура USB4

Към настоящия момент (2020 година)

вече сме свидетели USB4, стандарт който гарантира скорост на трансфера до 40[Gib/s].

https://en.wikipedia.org/wiki/USB4 .

Организацията USB Promoter Group, която поддържа стандартите на този последователен интерфейс, представи спецификациите на USB4 в края на 2019 година. Архитектурата на USB4 се базира на спецификациите на протокола Thunderbolt, предоставен от компания Intel, заедно с вече съществуващите архитектури USB 3.2 и USB 2.0. Този протокол позволява да се удвои пропускателната способност на USB, като предоставя възможност за едновременно използване на различни протоколи за предаване на данни. Новата архитектура дефинира метод за съвместно използване на една линия за връзка с няколко устройства.

Ключовите характеристики на USB4 включват:

· Дуплексна работа с приложение на кабели от тип USB Type-C със скорост до 40[Gib/s] и повече ;

· Едновременно използване на няколко протокола за предаване и изобразяване на данните за ефективно съвместно използване на общата шина ;

· Обратна съвместимост с USB 3.2, USB 2.0 и Thunderbolt 3.

Интерфейсът Thunderbolt изначално се разработвал за обединяване на различни мобилни устройства към нотбук и десктоп компютри с помощта на колкото се може по-малко кабели. Стандартът включва специален разединител за монитори и външни памети, при което осигурява мощност на захранването до 10[W], което е три пъти повече в сравнение с осигуряваната от USB 3.0 мощност (до 5[W]).

Интерфейсът Thunderbolt обединява протоколите на PCI Express (PCIe) и DiplayPort (DP) в един последователен сигнал, като предоставя постоянно напрежение по същия кабел. Контролерите Thunderbolt мултиплексират няколко даннови канала от подключените към тях устройства, използвайки един дуплексен канал. Сигналите се демултиплексират на противоположната страна. Един Thunderbolt порт може да поддържа до 6 устройства от същия тип, които се подключват през концентратори (Hub) или чрез дейзи верижка (Daisy chain).

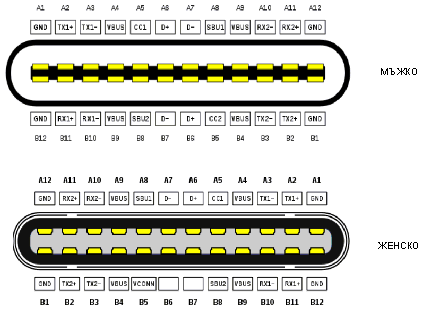

Активните Thunderbolt кабели съдържат специални интегрални схеми, вградени в корпуса на разединителя. Кабелът съдържа 5 проводника – един за управление и две еднопосочни кабелни двойки, съответно за входящия и за изходящия трансфер. Интерфейсът Thunderbolt използва разединител тип USB Type-C, показан на рисунката по-долу.

USB дърво

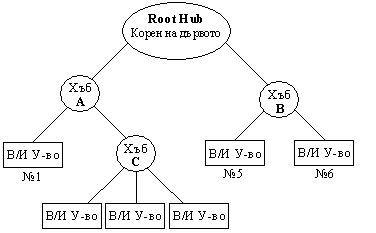

За да се осигури изискването за голям и динамичен състав на периферни устройства, концепцията за USB шината е дървовидна (известна още като топология “звезда”), както е показано на фигура 5.5.3.2.2.

Фиг. 5.5.3.2.2. Структура на USB-дърво

Към всеки изход от корена може да се подключва друг хъб или входно-изходно устройство. Когато потребителят подключи ново USB-устройство то се опознава от корена на системата, който генерира прекъсване към операционната система. Тя от своя страна идентифицира интерфейсните възможности на новото устройство, присвоява му съответния адрес и записва в неговите конфигурационни регистри необходимата информация.

В нормален режим хъбът в последната точка копира полученото входно съобщение в своите изходни портове. Така изпратеното от корена съобщение попада във всички подключени към него входно-изходни устройства, но на това съобщение отговаря само онова устройство, което е разпознало своя адрес. Така стандартът USB реализира принципа “който първи се е събудил, на него се полагат чехлите”. В обратната посока нещата са различни - съобщенията на входно-изходните устройства се изпращат само нагоре по дървото, в посока към корена. Така съобщението от едно устройство не се наблюдава от останалите устройства в дървото. По този начин коренът на дървото може да комуникира с всяко от устройствата, но не им позволява да комуникират помежду си.

При организиране на функционирането на USB-дървото се приема още, че подключените устройства не са инициативни. Едно устройство може да изпрати съобщение нагоре по дървото към хоста (корена) само в отговор на негово съобщение. По този начин изпращаните към хоста съобщения не се пресичат и не конфликтуват, тъй като едновременното изпращане на съобщения от две и повече устройства е невъзможно.

Този начин на функциониране е удобен за по-бавните устройства, но за тези с интерфейс USB 2.0 не е. Ще поясним това с пример върху фигура 5.5.3.2.2. Разглеждаме хъб В, към който са подключени две устройства – устройство №5, което е високо скоростно и устройство №6, което е ниско скоростно. Нека коренът на дървото да има интерфейс USB 2.0. Първоначално можем да приемем, че съобщенията за ниско скоростното устройство №6 се изпращат от корена с ниска скорост. При скорост от 1,55[Mib/s] обаче изпращането дори на кратко съобщение би му отнело времеви интервал, който е от порядъка на няколко десетки милисекунди. По време на този интервал други данни не могат да се прехвърлят, което окачествява цялостния трансфер по дървото като много бавен, с големи задръжки, което не е приемливо за бързите устройства. Това определено е проблем, който произлезе от предположението, че съобщенията от корена към устройствата могат да бъдат съобразени с тяхното собствено бързодействие. Окончателно се налага изводът, че съобщенията на коренния хъб по високоскоростните връзки следва да достигат хъба на устройството с максимална скорост. На последния етап устройството получава съобщението от своя хъб със съответната му скорост. Дори този етап да е много продължителен, той не би попречил на съобщенията по високо скоростната връзка с бързото устройство №5. Така високо скоростната шина между корена и хъб В се дели между двете устройства, подключени към него. За целта съобщенията към бавното устройство №6 се обменят заедно с авангардни и ариергардни предупреждаващи неговия хъб команди, за това, че трафикът му е разцепен.

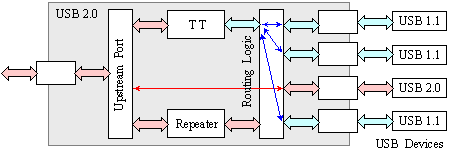

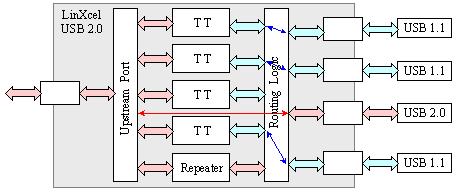

За преодоляване на проблема с ниската скорост на устройства с интерфейс USB 1.1 в състава на дървото могат да се включат допълнителни високо скоростни концентратори. Всеки USB 2.0 хъб съдържа в структурата си поне един транслатор на транзакции (ТТ), който разпознава интерфейса на устройствата и оптимално привежда транзакциите от бавните устройства в бързи и обратно. Бързото устройство, което е подключено към един от портовете се обслужва директно (фигура 5.5.3.8). Останалите три бавни устройства се обслужват от транслатора ТТ. Наличието обаче само на един транслатор за всички устройства ограничава пропускателната способност на цялата система до възможностите на интерфейса USB 1.1.

Фиг. 5.5.3.2.3. Концентратор с едно ТТ-устройство

Ето защо са разработени концентратори, съдържащи транслатор на транзакции за всеки USB порт. При същата конфигурация всеки транслатор ще обслужва отделно устройство. Тъй като бързото устройство не използва транслатор и се обслужва директно, то един от транслаторите в показаната конфигурация не се използва.

Фиг. 5.5.3.2.4 Концентратор с ТТ-устройство за всеки порт

Проблемът с производителността е бил известен още в самото начало на стандарта, ето защо за да се структурира данновия поток в съответствие с пропускателната способност на USB-устройствата са разработени следните под-протоколи, наричани още кадри: bulk (масивен), control (управляващ), interrupt (прекъсване) и isochronous (изохронен).

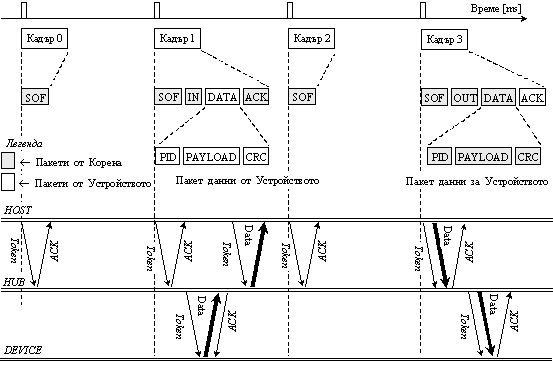

USB-дървото функционира по следния начин: през 1[ms] коренът на дървото генерира нов кадър за да синхронизира работата на всички устройства във времето. Кадърът съдържа пакети, първият от които се предава винаги надолу по дървото (от концентратор към устройство) и се нарича SOF (Start Of Frame). Следващите пакети в кадъра могат да се предават в същата посока или в обратната – от устройството към хъба.

Пакетът SOF има следната структура:

SOF :: <PID> <ADDR> <ENDP> <CRC5>

в която полетата имат съответно дължините 8, 7, 4 и 5 бита.

Осем битовото поле PID съдържа правата и инверсната фаза на идентификатора на пакета:

<PID0><PID1><PID2><PID3><notPID0><notPID1><notPID2><notPID3>.

Така се различават 16 вида пакети. 16-те вида пакети се групират в 4 типа, показани в таблица 5.5.3.2.1. В таблицата са дадени техните означения, десетичните и двоичните им кодове:

Таблица 5.5.3.2.1 Типове на пакетите

|

Маркер |

Данни |

Диалогови |

Специални |

|

OUT (1=0001) |

DATA0 (3=0011) |

ACK (2=0010) |

PRE (12=1100) |

|

IN (9=1001) |

DATA1 (11=1011) |

NAK (10=1010) |

ERR (12=1100) |

|

SOF (5=0101) |

DATA2 (7=0111) |

STALL (14=1110) |

SPLIT (8=1000) |

|

SETUP (13=1101) |

MDATA (15=1111) |

NYET (6=0110) |

PING (4=0100) |

|

|

|

|

Reserve (0=0000) |

Някои управляващи пакети, като ACK (потвърждение) съдържат само байта PID. След полето PID следва 7-битовото поле ADDR – адрес на устройство. След него следва номерът на крайната точка ENDP в самото устройство. Последните 5 бита съдържат контролната комбинация на циклическия код CRC (Cyclic Redundancy Check) за предидущото 11-битово поле.

Кадрите, които генерира корена, съдържат различен брой пакети (един или няколко, като първият е винаги SOF). Пакетите могат да се разпространяват и в двете посоки.

Данновите пакети имат следната структура:

DATA :: <PID> <PAYLOAD> <CRC16>

в която полето PID заема 8 бита, полезната част на пакета PAYLOAD може да бъде с дължина от 0 до 8192 бита. Максималната скорост на интерфейса обаче ограничава тази дължина до 1023 бита. И накрая 16-битовото поле CRC съдържа контролния код на полезната (данновата) част от пакета.

Трафикът на кадрите, разпространяващи се между корена и устройствата може да бъде представен, както е показано на фигура 5.5.3.2.5:

Фиг. 5.5.3.2.5. Времедиаграма на трафик

USB системите са многослойни системи и всеки слой има своята същност:

1. Слой Bus Interface. Интерфейсът на шината осигурява физическата, сигналната и пакетната връзка между корена и устройствата.

2. Слой Device. Крайните USB-устройства използват пакетна организация за базовите USB-операции чрез шината. Това позволява на корена да определи характеристиките на устройствата. Включително техния клас, името на производителя, името на устройството (модел), изискванията към захранващото напрежение и много други.

3. Слой Function. Този слой предоставя допълнителни възможности, специфични за устройството.

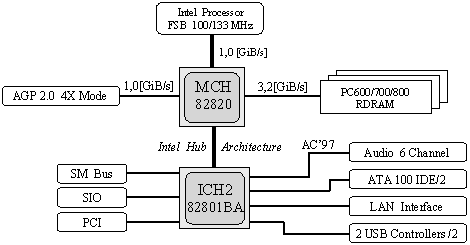

В хъбовата архитектура на системните платки, чието реализиране започва с чипсетите от серията i800, северният мост (North Brodge) започва да се нарича Memory Controller Hub (MCH). В същото време, южният мост South Bridge, започва да се нарича I/O Controller Hub (ICH). Връзката между двата хъб-компонента е специална – високоскоростен хъб-интерфейс. Така хъбовата архитектура на входно-изходната система притежава следните предимства:

· Увеличена пропускателна способност;

· Снижено натоварване на системната PCI-шина;

· По-проста монтажна схема.

Хъб-архитектурата предвижда увеличена пропускателна способност на PCI-устройствата, което се дължи на отсъствието на южния мост, който товари PCI-шината с трансфера от схемата Super I/O. Благодарение на това, че хъб-архитектурата заобикаля PCI-шината, се осигурява по-висока пропускателна възможност за устройства, които са подключени към I/O Controller Hub, към който пък са подключени новите устройства с интерфейс ATA-100 и USB 2.0.

На следващата фигура е показана архитектурата на система на базата на чипсет i810 – първият чипсет с тази архитектура.

Фиг. 5.5.3.2.6. Структура на хъбова архитектура (Intel Hub Architecture i810)

Северният хъб от чипсета изпълнява същите функции, каквито изпълнява и северния мост в шинно-мостовата архитектура. Той свързва шината на процесора с оперативната памет, както и графичния контролер чрез AGP-порта. В южна посока обаче вече не се намира PCI-шината, а високо производителен интерфейс – връзка с южния хъб. Междухъбовият интерфейс AHA (Accelerated Hub Architecture) е 8 битов, работи на честота 66[MHz], извършва 4 трансфера за един такт, с което осигурява скорост на обмена от 266[MiB/s]. Междухъбовият интерфейс има още една разновидност, наречена DMI (Direct Media Interface), представляваща PCI Express връзка с 4 линии с по 4 бита. Интерфейсът използва две отделни еднопосочни връзки, като данните се предават едновременно и в двете посоки (дуплексен режим). Във всяка посока пропускателната способност е 1[GiB/s], т.е. 250[MiB/s] x4 линии. Така за двете посоки се получава 2[GiB/s], което е до 14 пъти по-бързо от PCI. Производителят на дънни платки VIA именува междухъбовата връзка V-Link.

Тясната шина на хъбовия интерфейс поражда по-малко електрически смущения, което позволява прилагането на по-високи тактови честоти. В резултат се постига по-висока пропускателна способност и икономичност, в сравнение с шинно-мостовата архитектура.

Предимствата на хъбовата архитектура са следните:

· Висока скорост на трансфер в междухъбовата връзка ;

· Води до намалено натоварване на PCI шината. Хъбовият интерфейс е независим от PCI шината и не завзема нейния капацитет, което води до висока пропускателна способност на PCI устройствата, тъй като PCI шината не обслужва южния мост ;

· Тъй като заобикаля PCI шината, хъбовата архитектура позволява по-висока пропускателна способност и за устройства, които са свързани директно към Super I/O чипа, каквито са интерфейсите ATA, SATA, USB 2.0 ;

· Намалява опроводяването на дънната платка. Хъбовият интерфейс е широк 8 бита и изисква 15 сигнала за да бъде реализиран на дънната платка. DMI е широк само 4 бита и използва 8 диференциални двойки. В същото време 32 битовата PCI шина използва 64 сигнала ;

· LPC шината (Low Pin Count), която свързва BIOS (вижте по-долу на следващата фигура), има максимална пропускателна способност от 16,67[MiB/s], която е по-бърза и съдържа само 13 сигнала.

Високоскоростната шина, свързваща двата моста се именова от отделните производители различно. Така например, в наборите на SiS тя е наречена MuTIOL, в наборите на VIA е наречена V-Link, а в тези на Uli (бившата Ali) се нарича Hyper Transport.

С

появата на новата шина PCI Express северният хъб (мост) не се е променил

съществено – вместо AGP се предлага високо скоростен порт x8 или x16 или PCI

Express. Ако външните интерфейси, които чипсетите предлагат, съответстват на

общоприетите и стандартни шини, то междухъбовата връзка се изгражда от шина,

собствена разработка на съответната фирма.

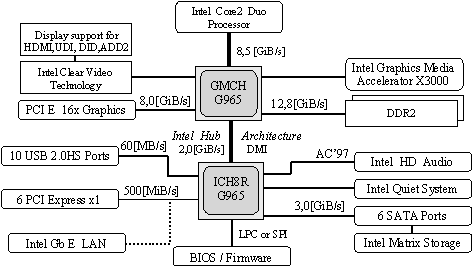

Фиг. 5.5.3.2.7. Структура на хъбова архитектура (Intel Hub Architecture i965)

GMCH – Graphics Memory

Controller Hub ;

ICH – I/O

Controller Hub .

Кратко ще изброим основните функционални характеристики на серията чипсети 965:

· Поддържа всички “стари” процесори от фамилията Celeron и Pentium (включително двуядрените) с честота на системната шина 533/800/1066 [MHz], а така също всички процесори Core 2 Duo/Extreme;

· Съдържа двуканален контролер на паметта DDR2 533/667/800 и поддържа до 4 модула DIMM с общ обем до 8[GiB] и технологиите Fast Memory Access и Flex Memory;

· Притежава графичен интерфейс PCI Express x16;

· Съдържа интегрирано графично ядро GMA X3000 с поддръжка на технологията Clear Video;

· Има шина DMI (Direct Media Interface) (с пропускателна възможност 2[GiB/s]) за връзка с южния мост ICH8R;

· Поддържа до 6 порта PCI Express x1 и до 4 слота PCI;

· Поддържа 6 порта Serial ATA II (SATA II – второ поколение стандарта);

· Възможност за организация на RAID-масив с нива 0 и 1;

· Съдържа два високо скоростни хост-контролера EHCI с 10 USB 2.0 слота;

· МАС-контролер Gigabit Ethernet и специален интерфейс (LCI/GLCI) за включване на PHY-контролер (i82566 Gigabit Ethernet, i82562 за Fast Ethernet);

· Интерфейс High Definition Audio (7.1);

· Поддържа също ниско скоростната и остаряла периферия.

Чипсетът от началото на 2007 година на компанията Intel е обозначен i975. Той се състои от две интегрални схеми – MCH (i82975X Memry Controller Hub) и ICH (i82801GR I/O Controller Hub ICH7R). Северният мост се подключва чрез FSB-шина (от типа Quad-Pumped Bus) към процесори от моделите Intel Pentium 4, Intel Pentium 4 Extreme Edition, както и следващите двуядрени процесори, включително процесорите с технологията Hyper-Threading с тактова честота на процесорната шина 266/200 [MHz]. Тактовата честота на чипсета е 133/100 [MHz].

Процесорната шина поддържа 36-битов адрес, с което се осигурява 8[GiB] обем на оперативната памет.

Двете интегрални схеми на чипсета комуникират чрез DMI-шина (Direct Media Interface), осигуряваща пълен дуплекс със скорост на трансфер 2[GiB/s] в двете направления.

Интегрираният в северния хъб контролер на паметта може да работи както в едноканален, така и в двуканален режим. Контролерът поддържа само DDR2 SDRAM (533/667) [MHz]. За подсистемата на паметта е реализирана фирмена технология за допълнително повишаване на производителността, наречена Intel Memory Pipeline Technology.

Вградените в южния хъб интерфейси и функции са:

·

Един канал IDE с поддръжка АТА 33/66/100 [MHz] (до 2

устройства) ;

·

4 порта Serial ATA 300 (SATA II, до 300 [MiB/s]) ;

·

8 порта USB 2.0 ;

·

4 порта PCI Express x1;

·

6 порта PCI 2.3 (32 [b], 33 [MHz]) ;

·

Шина LPC (Low Pin Count) ;

·

Контролер Intel High Definition Audio, поддържащ 3

кодека ;

·

Шина АС’97 2.3 с 8 канала ;

·

Интегриран LAN-контролер (10/100/1000 [Mib/s] Ethernet) ;

·

Шина SMBus ;

·

Контролери на прекъсвания APIC, APIC 2.0 ;

·

Поддържа функция RAID (RAID 0, 1, 0+1, 5).

Структурата на компютърна система на базата на този чипсет има вид подобен на представения на фигура 5.5.3.2.7.

С кратко представените примерни реализации ние приемаме, че сме пояснили този вид архитектура на входно-изходната система. Еволюцията не може да бъде спряна и читателят може да проследи нейното развитие, в което ще му помагат изложените тук принципни положения.

Следващият

раздел е:

5.5.3.3 Архитектура

“Hyper Transport” на входно-изходната система